# **LOGIC ANALYZERS**

# **State and Timing Analysis Modules**

HP 16550A, 16554A, 16555A, 16556A, 16555D, 16556D

### **Key Specifications and Characteristics**

|                           | HP 16550A                                                                                           | HP 16554A1                                | HP 16555A/16555D1                                                       | HP 16556A/16556D1                                         |

|---------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|

| Timing-analysis rate      | Conventional: 250/500 MHz <sup>2</sup><br>Transitional: 125/250 MHz <sup>2</sup><br>Glitch: 125 MHz | Conventional: 125/250 MHz <sup>2</sup>    | Conventional: 250/500 MHz <sup>2</sup>                                  | Conventional: 200/400 MHz <sup>2</sup>                    |

| State-analysis rate       | 100 MHz                                                                                             | 70 MHz                                    | 110 MHz <sup>3</sup>                                                    | 100 MHz                                                   |

| Channels/card             | 102                                                                                                 | 68                                        | 68                                                                      | 68                                                        |

| Channels/timebase         | 204                                                                                                 | 204                                       | 204                                                                     | 340                                                       |

| Memory depth/channel      | 4 K/8 K <sup>4</sup>                                                                                | 512k/1024K <sup>4</sup>                   | 1M/2M <sup>4</sup> , 2M/4M <sup>4</sup>                                 | 1M/2M <sup>4</sup> , 2M/4M <sup>4</sup>                   |

| Setup/hold time           | 3.5/0 ns to 0/3.5 ns adj. in<br>500 ps steps                                                        | 3.5/0 ns to 0/3.5 ns adj. in 500 ps steps | 3.5/0 ns to 0/3.5 ns adj.<br>500 ps steps                               | 3.5/0 ns to 0/3.5 ns adj. in<br>500 ps steps              |

| Minimum detectable glitch | 3.5 ns                                                                                              | 3.5 ns                                    | 3.5 ns                                                                  | 3.5 ns                                                    |

| Probe input R and C       | 100k Ω and ~ 8 pF                                                                                   | 100k Ω and ~ 8 pF                         | 100k Ω and ~ 8 pF                                                       | 100k Ω and ~ 8 pF                                         |

| Triggering terms          | ggering terms Patterns: 10; Ranges: 2; Patterns: 10°; Ranges: Edge and glitch: 2; Timers: 2         |                                           | Patterns: 10 <sup>5</sup> ; Ranges: 2;<br>Edge and glitch: 2; Timers: 2 | Patterns: 10; Ranges: 2;<br>Edge and glitch: 2; Timers: 2 |

| Trigger sequence levels   | 12 in state and 10 in timing                                                                        | 12 in state and 10 in timing              | 12 in state and 10 in timing                                            | 12 in state and 10 in timing                              |

| Symbols                   | Unlimited                                                                                           | Unlimited                                 | Unlimited                                                               | Unlimited                                                 |

PHP 16554A, 16555A, 16555D, 16556A, and 16556D can only be used with the HP 16500B or 16500C logic analysis mainframe.

### State and Timing Analysis with a Choice of Depth

The HP 16550 series of state and timing analyzers offers a range of memory depths and state analysis speeds to fit your application. The HP 16550A offers industry-standard state and timing analysis features at an affordable price. The HP 16554A, 16555A, 16556A, and the new HP 16555D and 16556D analyzers provide the same acquisition and triggering capabilities as the HP 16550A, but provide the deeper memory needed to capture elusive system crashes.

All HP 16550 series analyzers use the same probing scheme, which makes it possible for you to easily interchange probing interconnections whenever your probing needs change. All HP 16550 series analyzers also connect to Hewlett-Packard's broad and growing selection of preprocessor solutions because the probes are compatible with previous HP state and timing analyzer modules.

#### **Capture State or Timing Data on All Channels**

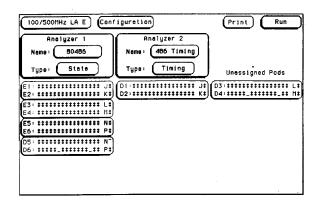

With the HP 16550 series of state and timing analyzers, there is no need to connect special probes to view timing activity. All channels on HP state and timing analysis modules perform either state or timing functions. Set up your HP 16550 series analyzer to perform simultaneous, fully time-correlated state analysis on some channels, and timing analysis on the rest.

Assign channels to capture state timing data without moving probes

## Advanced Trigger Macros Capture Elusive Problems

Both basic and complex state and timing macros are available in the trigger macro library. Macros can be combined to create custom trigger setups.

|            |                                               | terna           |  |  |  |

|------------|-----------------------------------------------|-----------------|--|--|--|

| Macro Type | Trigger Macro                                 |                 |  |  |  |

|            | + MORE +                                      |                 |  |  |  |

| Besic      | 1. Find anystate n times                      | 1               |  |  |  |

| Macros     | 2. Find pattern present/absent for > duration | 1               |  |  |  |

|            | 3. Find pattern present/absent for < duration | 4-5             |  |  |  |

|            | 4. Find edge                                  | 1               |  |  |  |

|            | 5. Find Nth occ. of en edge                   | 1               |  |  |  |

| Patt/Edge  | 1. Find edge within a valid pattern           | 2               |  |  |  |

| Combos     | 2. Find pattern accurring too soon after edge | 2<br>3-4        |  |  |  |

|            | 3. Find pattern occurring too late after edge | 2               |  |  |  |

| Time       | 1. Find 2 edges too close together            | 3-4             |  |  |  |

| Yioletions | 2. Find 2 edges too for opert                 | 3-4<br>2<br>4-5 |  |  |  |

|            | 3. Find width violation on a pattern/pulse    | 4~5             |  |  |  |

|            | + MORE +                                      |                 |  |  |  |

| Cancel     | Internal Levels Remaining = 10 Do             | 10              |  |  |  |

The HP 16550 series timing trigger macro library.

Each trigger macro has a graphic of the measurement and a sentence-like structure to make triggering easy. Set up your triggering in terms of the measurement you want to make, rather than in terms of the trigger functions in the logic analyzer.

Families of trigger macros make it easy to pick out just the trigger macro you need, and avoid the hassle of wading through a long list of triggers to find the one you want. Families of trigger macro measurements include:

- Basic macros, including find anystate n times;

- Sequence-dependent macros, including find a n-bit serial pattern;

- Time-violation macros, including find an event 2 occurring too soon after event 1.

<sup>&</sup>lt;sup>2</sup>Half-channel mode doubles memory depth, doubles maximum conventional timing speed and doubles maximum transitional timing speed.

For 110-MHz mode only-Single clock edge with qualifiers. 100-MHz mode and below is the same as the HP 16550A.

<sup>&#</sup>x27;Memory depth doubles in half-channel timing mode

Eight pattern recognizers are available in HP 16554A timing modes and HP 16555A/16555D timing and 110-MHz state analysis modes.

State and Timing Analysis Modules (cont'd) HP 16550A, 16554A, 16555A, 16556A, 16555D, 16556D

Insert Level Select New Hacro Sequence Level 1

Find pattern occurring too eon efter edge

Find pattern o occurring within 16 ns efter edge edgel

adgel occurring within 16 ns of ter edge occurring within 16 ns of ter edge occurring edgel

Typical timing trigger macro input screen.

## **Analyze Distant Timing Events with Transitional Timing**

Capture events that are seconds apart while maintaining 4-ns resolution with the HP 16550A. Transitional timing samples at full speed but only stores data when a transition occurs. This technique effectively extends the total time captured by the acquisition memory while maintaining high time resolution.

Display timing measurements with bus values overlaid in the waveforms

### Track Problems in Multiprocessor and Multiple Bus Systems

Configure your HP 16550 series logic analyzer as two independent state analyzers that sample data using separate clocks. Time tagging of states lets you time-correlate and view the state listing interleaved on the same screen.

|    | 100/500MHz LA E Listing 1 Invasm Print Run |              |                |                      |      |                                    |            |

|----|--------------------------------------------|--------------|----------------|----------------------|------|------------------------------------|------------|

|    | Herkers<br>Time                            | $\mathbb{C}$ |                | g ta X<br>093 ms     |      | Trig to 0 X to 0 5.265 ms 1.175 ms |            |

| ľ  |                                            | 680          | 00             | ]                    |      |                                    |            |

| r  | Lebel>                                     | HPI          |                | Time                 | HPID | DATA (103116 GP Probe              | <b>s</b> ) |

| L  | Base>                                      | ASC          | II             | Absolute             | Hex  | 68000 Mnemonics / Hex              |            |

| Γ  |                                            | D            | D              | 3.508 ms             |      | xx44 user data urite               |            |

|    | 9 6                                        | I            | Ī              | 3.509 ms<br>4.088 ms | 44   | xx49 user data write               |            |

| 1  | 10                                         | 5            | - <del>-</del> | 4.093 ms<br>4.678 ms | 49   | xx53 user data urite               |            |

| L  | 11                                         | _K           | K              | 4.681 ms<br>5.268 ms | 53   | xx4B user data urite               |            |

| F  | 12                                         |              | K              | 5.269 ms<br>5.050 ms | 48   | xx20 user data write               |            |

| 1  | 12<br>13                                   | D            | D              | 5.659 ms<br>6.438 ms | 20   | xx44 user date write               |            |

| 1  | 14                                         | I            | D              | 6.443 ms<br>7.026 ms | 44   | xx49 user date write               |            |

| ľ  | 14<br>15                                   | R.           | Į<br>R         | 7.030 me<br>7.618 me | 49   | xx52 user date write               |            |

| 1_ | 15                                         |              | R              | 7.619 ms             | 52   |                                    |            |

View interactions between two separately clocked systems.

#### Capture Up to 340, 2M Deep Channels Simultaneously

Use the new HP 16555D and 16556D and the 16554A, 16555A and 16556A to debug ASICs, 8-bit, 16-bit, 32-bit and 64-bit microprocessors. Connect five HP 16556D cards for 340-channel wide measurements. The HP 16555D and HP 16556D provide 2M of acquisition memory across all channels. The HP 16555A and 16556A provide 1M of acquisition memory while the HP 16554A provides 512K.

The memory depth of all cards is doubled in timing analysis halfchannel mode.

### **Find Intermittent Errors Using Postprocessing**

In state mode, set up compare mode to "run until compare not equal" to capture intermittent errors. Use compare for quick go/no-go testing of your product in manufacturing. State compare shows you the effects of system changes by comparing each sample in the current measurement to each sample in the previous measurement. In timing mode, capture intermittent setup and hold violations using the specify-stop-measurement feature to repetitively acquire data until the time interval between two patterns violates a specified condition.

### **Enhance Troubleshooting with Flexible Display Modes**

State and timing analyzers let you display state measurements in listings, X-Y chart, or state waveforms. In addition to the waveform display, the HP 16550A, 16554A, 16555A/D, and 16556A/D allow you to display timing information as a listing. Markers placed on one display are automatically updated in the other display modes.

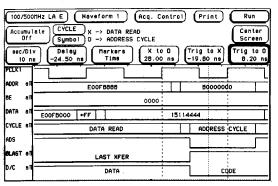

#### Find Whether the Problem is in Software or Hardware

Arm the timing analyzer with the state analyzer to capture system behavior between states. Display both measurements on one screen and use time-correlated markers to identify the cause of problem states.

Display time-correlated state and timing measurements on the

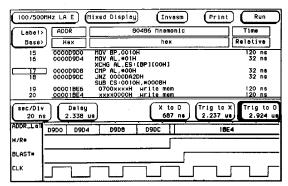

#### Analyze Your Software with Informative Listings

New technology allows you to filter the disassembled trace, so it's easier to analyze. For example, suppress the display of instructions that were prefetched, but not executed. Display your high-level symbols in the state listing. If you program in a high-level language, the optional HP E2450A symbol utility lets you import symbols from source code. The utility reads industry-standard object module formats.

| TH Semple LA I Listing 1 (Invesm Options) (Print) Run  Herkers Acquisition Time 19 Apr 1994 09:01:10 |                   |                      |                                 |                                          |  |

|------------------------------------------------------------------------------------------------------|-------------------|----------------------|---------------------------------|------------------------------------------|--|

| Label>                                                                                               | ADDR              |                      |                                 | P54C/CM Inverse Assembly                 |  |

| Base>                                                                                                | Symbo1            | Mnemonics/Hex        |                                 |                                          |  |

| 4212                                                                                                 | :get_message+006C | C0<br>C4<br>C7       | HOV<br>HOV                      | AX,[BX+0154]<br>BX,[BP+06]<br>[BX+10],AX |  |

| 4214                                                                                                 | :get_message+0074 | CA                   | HOV                             | AX,#0014<br>#ORD PTR [8P+04]             |  |

| 4216                                                                                                 | :get_message+007C | D0<br>D2             | HOV                             | BX,AX<br>[BX+0142],#0000                 |  |

| 4219                                                                                                 | :get_message+0084 | D8<br>D9<br>DA<br>DC | POP<br>POP<br>HOV<br>POP<br>RET | SI<br>DI<br>SP, BP<br>BP<br>NEAR         |  |

| 4235                                                                                                 | display_requ+0024 | D4<br>D6             | JLE                             | display_+00000018<br>[SI+03].DH          |  |

| 4237                                                                                                 | display_requ+002C | D9<br>DC             | JHP                             | display_+0000003D<br>Ax,#0002            |  |

Disassembly filters let you analyze software from multiple view-points. The symbol utility lets you import and display symbols from your software.

### **Key Literature**

A Family of State and Timing Analyzers for the HP 16500C Logic Analysis System, p/n 5962-7245E